ASRock

Menü

Menü

Wir verwenden Cookies, um Ihnen ein individuelles und reibungsloses Erlebnis zu bieten.

Wenn Sie diese Website besuchen, stimmen Sie unserer Verwendung von Cookies zu. Wenn Sie es vorziehen, keine Cookies zu akzeptieren oder weitere Informationen benötigen, lesen Sie bitte unsere Datenschutzerklärung.

![SA [0 Header-Hairline]](/mb/features/SA.png)

![SA [XXL Aluminum Alloy Heatsink]](/mb/features/SA-Heatsink-B550M Pro4.jpg)

![SA [Sapphire Black PCB]](/mb/features/SA-BlackPCB.jpg)

![SA [High Density Glass Fabric PCB]](/mb/features/SA-HDPCB.jpg)

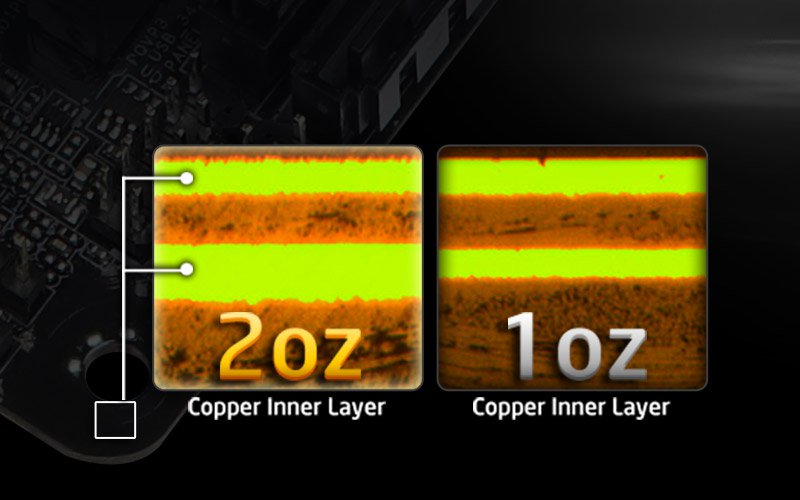

![SA [2oz Copper PCB]](/mb/features/SA-2oz.jpg)

*Supported only with processors with integrated graphics. Please check CPU support list from each motherboard webpage.

Die Begriffe HDMI und HDMI High-Definition Multimedia Interface sowie das HDMILogo sind Marken oder eingetragene Marken von HDMI Licensing Administrator, Inc. in den Vereinigten Staaten und anderen Ländern.

Die Spezifikationen können ohne vorherigen Hinweis geändert werden. Die Marken und Produktnamen sind Schutzmarken der jeweiligen Firmen. Alle Konfigurationen die von den original Spezifikationen abweichen werden nicht garantiert.

Das oben abgebildete User-Interface ist ein Referenzbeispiel. Das tatsächliche User-Interface kann von der Abbildung abweichen.